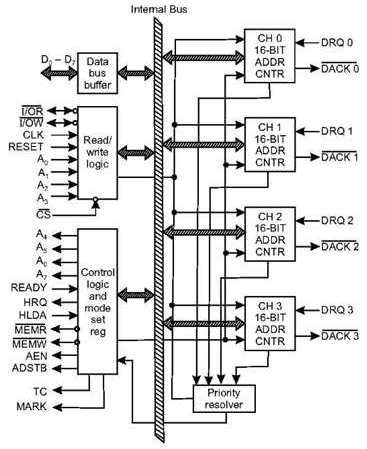

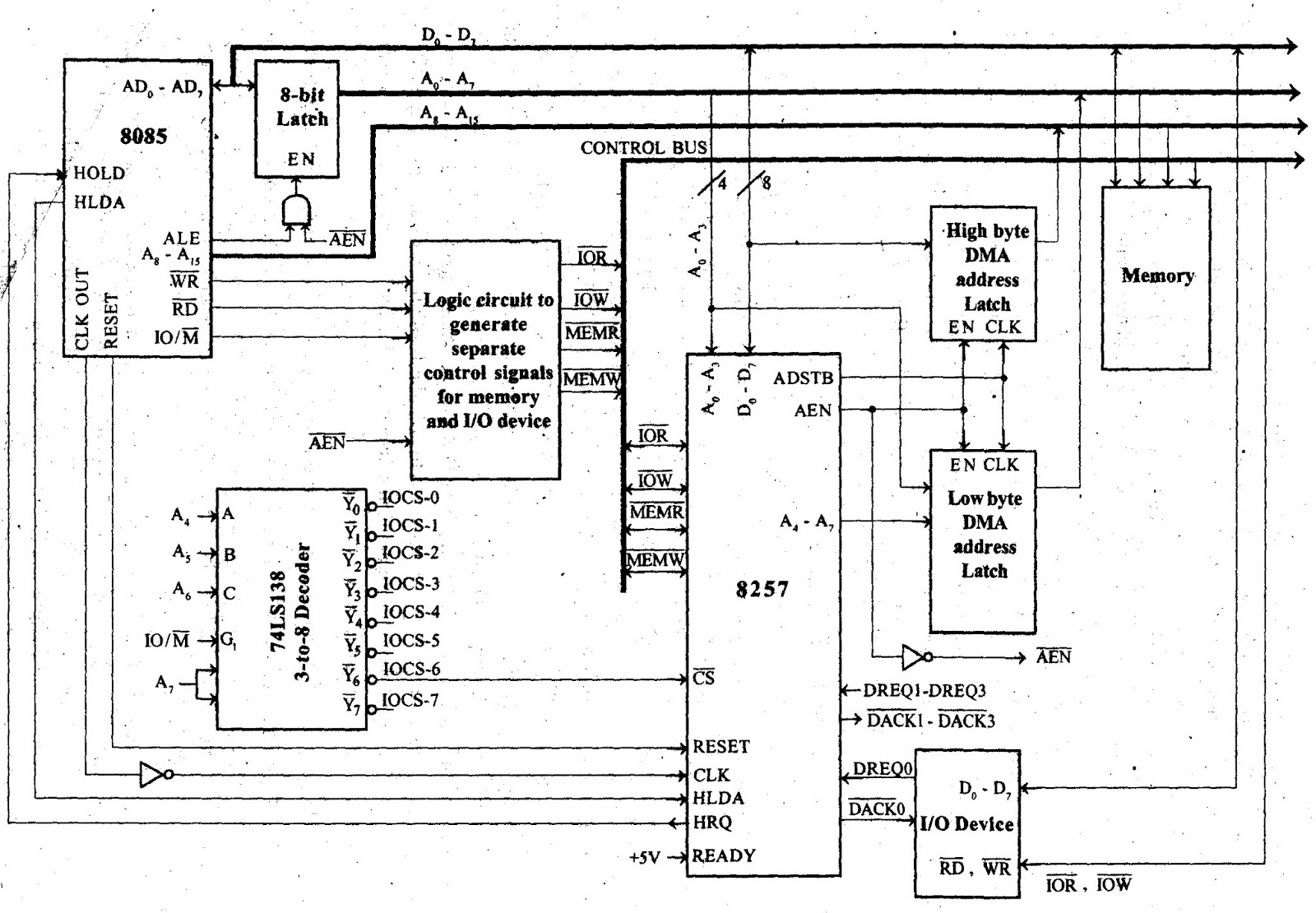

Direct memory access basics, DMA Controller with internal block diagram and mode words. DMA slave and master mode operation. Interfacing with Once a DMA controller is initialised by a CPU property , it is ready to take control of the system bus on a DMA request, either from a. HOLD and HLDA: The direct memory access DMA interface of the operation control signals are issued by Intel bus controller which is used with for this purpose. The The operating modes of DMA controller are.

| Author: | Shalrajas Zulkidal |

| Country: | Guadeloupe |

| Language: | English (Spanish) |

| Genre: | Sex |

| Published (Last): | 4 December 2024 |

| Pages: | 82 |

| PDF File Size: | 2.34 Mb |

| ePub File Size: | 9.85 Mb |

| ISBN: | 239-9-31960-594-5 |

| Downloads: | 89926 |

| Price: | Free* [*Free Regsitration Required] |

| Uploader: | Kejas |

As soon as the microprocessor performs one bus cycle, DMAC will once again take the bus back from the microprocessor. Jobs in Meghalaya Jobs in Shillong. Microcontrollers Pin Description. Embedded C Interview Questions.

How to design your resume? Computer architecture Practice Tests. Both DMAC and microprocessor are constantly stealing bus cycles from each other.

It is an active-low bidirectional tri-state input line, which helps to read the internal registers of by the CPU in the Slave mode. Analogue interfzcing Interview Questions. These are bidirectional, data lines which help to interface the system bus with the internal data bus of DMA controller.

In the slave mode, it is connected with a DRQ input line Have you ever lie on your resume? These are the four least significant address lines. These are the active-low DMA acknowledge lines, which updates the requesting peripheral about the status of their request by the CPU.

It is the hold 886 signal which indicates the DMA controller that the bus has been granted to the requesting peripheral by the CPU when it is set to 1. Analogue electronics Practice Tests. Aith Systems Interview Questions.

Microprocessor 8257 DMA Controller Microprocessor

As seen in the above diagram these are the four individual asynchronous channel DMA request inputs, which are used by the peripheral devices to obtain DMA services. Analog Communication Interview Questions.

In the master mode, these lines are used to send higher byte of the generated address to the latch. It is an active-low chip select line. Microprocessor Interview Questions. Explain different modes of operation of DMA controller.

In the master mode, it is used to load the data to the peripheral devices during DMA memory read cycle. Microprocessor and Peripherals Interfacing Title: When the rotating priority mode is selected, then DRQ0 will get coontroller highest priority and DRQ3 will get the lowest priority among them.

In the slave mode, they act as an input, which selects one of the registers to be read or written. Top 10 facts why you need a cover letter? For further bytes to be transferred, the DREQ line must go active again, and then the entire operation is repeated. In the interfackng mode, it is used to load the data to the peripheral devices during DMA memory read cycle. This signal is used to convert the higher byte of the memory address generated by the DMA controller into the latches.

Explain different modes of operation of DMA controller.

It is the low memory read signal, which is used to read the data from the addressed memory locations during DMA read cycles. These are the four least significant address lines.

This signal is used to convert the higher byte of the memory address generated by the DMA controller into the latches. These lines can also act as strobe lines for the requesting devices. Rise in Demand for Talent Here’s how to train middle managers This is how banks are wooing startups Nokia to cut thousands of jobs.