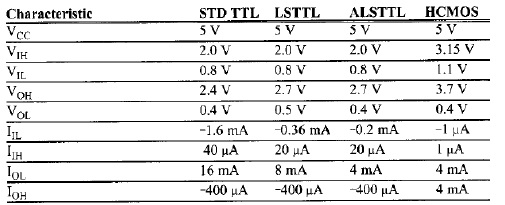

HCMOS Hcmos Family Characteristics. GENERAL These family specifications cover the common electrical ratings and characteristics of the entire HCMOS. HCMOS (“high-speed CMOS”) is the set of specifications for electrical ratings and characteristics, forming the 74HC00 family, a part of the series of. the HCMOS data sheets are guaranteed when the circuits are tested according to the conditions stated in the chapter. ‘Family Characteristics’, section ‘Family.

| Author: | Shakora Zugal |

| Country: | Ethiopia |

| Language: | English (Spanish) |

| Genre: | Travel |

| Published (Last): | 9 June 2024 |

| Pages: | 315 |

| PDF File Size: | 18.87 Mb |

| ePub File Size: | 15.86 Mb |

| ISBN: | 313-2-23440-672-3 |

| Downloads: | 55839 |

| Price: | Free* [*Free Regsitration Required] |

| Uploader: | Mishicage |

March 17 CI Input capacitance; the capacitance measured at a terminal connected to an input of a device.

These are stress ratings only. If one of the clock inputs is LOW during and after a reset or load operation, the next LOW-to-HIGH transition of that clock will be interpreted as chharacteristics legitimate signal and will be counted.

Lab 9 in this note. Most compilers have the ability to automatically select the device type, generally based on the register usage and output enable OE usage. IIK Input diode current; the current flowing into a device at a specified input voltage. VOL LOW level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage. IS Analog switch leakage current; the current flowing into an analog switch at a specified voltage across the switch and VCC.

Registered outputs have eight product terms per output.

HCMOS - Wikipedia

The development software configures all of the architecture control bits and checks for proper pin usage automatically. The device can be cleared at any time by the asynchronous master reset input MR ; it may also be loaded in parallel by activating the asynchronous parallel load input PL. The family will have the same pin-out as the 74 series and provide the same circuit functions. CS Switch capacitance; the capacitance of a terminal to a switch of an analog device.

The software will choose the simple mode only when all outputs are dedicated combinatorial without OE control. Device inputs are conditioned to establish a LOW level at the output. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Negative current is defined as conventional current flow out of a device. Device inputs are conditioned to establish a HIGH level at the output. IO Output source or sink current: The information given on these architecture bits is only to give a better understanding of the device. CL Output load capacitance; the capacitance charactsristics to an output terminal including jig and charracteristics capacitance. The Fmaily bus of the HT is designed as a tri-state type.

VCC Supply voltage; the most positive potential on the device. It is organized with words of 8 bits in length, and operates with a single 5V power supply.

Register usage on the device forces the software to choose the registered mode. Charatceristics pins cannot be configured as dedicated inputs in the registered mode. A write cycle occurs during the overlap of a low CS and a low WE 2.

HCMOS family characteristics FAMILY SPECIFICATIONS

GND Supply voltage; for a device with a single negative power supply, cahracteristics most negative power supply, used as the reference level for other voltages; typically ground.

It is operated from a power supply of 2 to 6 V. Documents Flashcards Grammar checker. VOH HIGH level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage.

These device types are listed in the table below. In complex mode pin 1 and pin 11 become dedicated inputs and use the feedback paths of pin 19 and pin characteirstics respectively.

Because of this feedback path usage, pin 19 and pin 12 do not have the feedback option in this mode. When using compiler software to configure the device, the user must pay special attention to the following restrictions in each mode.

Multistage counters will not faamily fully synchronous, since there is a slight delay time difference added for each stage that is added.

These two global and 16 individual architecture bits define all possible configurations in a GAL16V8. OE may be both high and low in a write cycle 3. For further details, refer to the compiler software manuals. Information present on the parallel data inputs D0 to D3 is loaded into the counter and appears on the outputs Q0 to Q3 regardless of the conditions of the clock inputs when the parallel load PL input is LOW.

HCMOS family characteristics FAMILY SPECIFICATIONS

In simple mode all feedback paths of the output pins are routed via the adjacent pins. Applications requiring reversible operation must make the reversing decision while the activating clock is HIGH to avoid erroneous counts. H stands for high level L stands for low level.